Volume: 01 Issue: 03 ISSN: 2582-3078

Available online at: http://www.jartms.org

# DESIGN AND IMPLEMENTATION OF HIGH SPEED HYBRID ADDER WITH REVERSE CARRY PROPAGATE ADDER

## P. RAMYA<sup>1</sup>, DR. V. THRIMURTHULU<sup>2</sup>, G. DILLIRANI<sup>3</sup>

<sup>1</sup>PG Scholar, Dept. of ECE, Chadalawada Ramanamma Engineering College, Tirupathi, AP, India, E-mail: patturamya95@gmail.com.

<sup>2</sup>Professor, Dept. of ECE, Chadalawada Ramanamma Engineering College, Tirupathi, AP, India, E-mail: <a href="mailto:vtmurthy.v@gmail.com">vtmurthy.v@gmail.com</a>.

<sup>3</sup>Assistant Professor, Dept. of ECE, Chadalawada Ramanamma Engineering College, Tirupathi, AP, India, E-mail: gdillirani@gmail.com.

#### **ABSTRACT:**

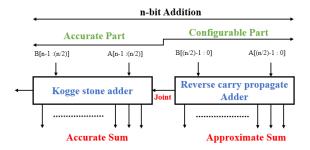

This paper helps us to discuss about approximate Reverse Carry Propagate Adder (RCPA), In RCP adders the carry signal propagates in counter down flow manner. I.e. it flows from the maximized prioritized bit to the least prioritized bit. Henceforth the carry i/p signal has the greater significance then the o/p carry. This way of carry propagation increases the steadiness in presence of delay versions, here in this paper we are discussing about the three different designs of RCPA cells with different delay, energy, and accuracy configurations, and also we use a few hybrid structure within the n bit adder design were least half of the adder design is carried out with this RCPA and most considerable half will be introduced by way of using some accurate high pace adder like KoggeStone adder that may decorate the adder speed. The Hybrid adders realized utilizing those systems are studied and as compared people with conventional approximate adders with Xilinx ISE 14.7 Verilog HDL coding.

**Keywords:** Approximate adder, Digital Signal Processing (DSP), Reverse Carry Propagate adder (RCPA), Kogge Stone adder (KSA)

#### I. INTRODUCTION

Adder blocks, which are probably the precept additives in arithmetic devices of DSP systems, are electricity hungry and frequently form hot-spot locations on the die. The ones facts were the motivations for understanding this factor the usage of the approximate calculating approach. Early researches on approximate adders have taken state-of-the-art procedures of that specialize in errors weight and blunders opportunity reductions. Power intake reduction and pace development are the important thing dreams within the layout of digital processing units, specially the portable structures. Normally, a growth inside the speed is carried out at the value of greater power intake for actual processing units. One of the procedures to improve both the energy and pace is to sacrifice the computation exactness. This approach, which is approximate computing, may be used for the applications in which a few mistakes maybe tolerated. The first technique is primarily based on a hybrid shape adder where in two different components, actual MSBs & LSBs are utilized. Within the carry i/p of the MSB element and summation of the LSB component the error occurs. Consequently this reduces the error weight to the load of the carry i/p of the MSB part. Given that usually maximum of the activities get up within the LSB. Inside the second approach, natural approximate adder systems are employed. For those adders, reducing the error possibility of the summation further decreases the strength and delay which are the important things in layout criteria. As per the flow of this paper, we have recognized that the Hybrid Adders in which the use

Available online at: http://www.jartms.org

of the approximate Reverse Carry Propagate complete-adder (RCPFA) is usually suggested. The approximate summing circuit propagates the i/p carry signal in a counter-down manner, i.e., from the higher remarkable bit to lower remarkable bit to form the bring o/p. on this form of adder this is known as Reverse Carry Propagate adder (RCPA) the propagation is finished via introducing a forecast signal appearing as an o/p signal, due to the alternative/opposite propagation, the weight of the carry decreases because it propagates. The MSB half of could be added with the assist of parallel prefix adder that can have better velocity of operation. Decrease component might be brought with the assist of approximate opposite carry propagate adder.

The structure of the paper is prepared as follows: In sector II we come across some related works which are briefly reviewed. Various designs of the proposed RCPFA are defined in sector III. The proposed approximate n-bit adder is proposed with approximate FAs in section IV. In section V we present the evaluation outcomes between proposed and current adder designs. Finally in section VI we conclude the paper

#### II. EARLIER WORK

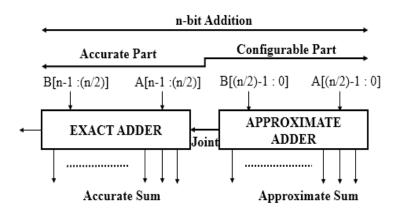

Ripple carry adder (RCA) has the lowest strength and area usage amongst all the precise adder structures, but it suffers from a huge delay. To enhance the velocity and electricity efficiency of this adder, some earlier works have sacrificed the accuracy. An approximate RCA shape which is also known as Error Tolerant adder structure (EAS) has been provided. The shape of EAS is shown in Fig. 1. On this structure, the i/P operands are divided into components known as precise computation part and inexact computation element. Within the real aspect is the MSB part, the traditional FAs with a zero carry i/p for the whole component are used while the inexact part is the LSB element which includes a carry-free addition element.

Fig.1 Error tolerant adder structure

Designing an adder with carry propagation will take more delay so if we avoid the carry propagation even as designing an adder will outcomes the better adder performance so we move for Reverse Carry Propagate adder in which the carry is propagated in contrary course. The formal full adder that's the necessary factor building block of the carry propagates adders has 3 i/ps with the identical weight. Moreover, it's outputs for a addition results with constant weight as that of the i/ps and a carry o/p with

DST Sponsored Three Day National Conference on "Sensor Networks, Internet of Things and Internet of Everything", 17 October 2019 to 19 October 2019 Organized by Department of EEE, Chadalawada Ramanamma Engineering College (Autonomous), A.P.

Available online at: http://www.jartms.org

times the load. The carry propagation delay (t\_CP) is that the most essential timing parameter in associate full adder because of the truth that it determines the delay of the very important path of multi bit adders (and multipliers).

A small short-delay violation to boot additionally bring on a colossal quantity of errors because of the reality that the error takes region at the MSBs of the summation. That's the top results of the time and propagation of the carry i/p of the MSBs through tiny monumental bit FAs. Primarily based all during this reasoning, if the order of the carry propagation is reversed, one may expect that the amount of errors because of the timing violation decreases.

# Reverse Carry Propagate Full-Adder Cell

Every specific FA generates its carry o/p and sum indicators the usage of

$$2C_{i+1} + Si = Ai + Bi + Ci \dots \dots \dots (1)$$

Where Ai(Bi) is the  $i^h$ th bit of the i/p A(B), Ci(Ci+1) is the carry i/p, and Si is the  $i^h$ th bit of the sum. Based in this equation, the o/p signal within the  $i^h$ th bit role relies upon on the  $i^h$ th bits of the i/p's A&B and the deliver o/p of the preceding function (Ci). Via shifting the term Ci(Ci+1) to the left (right) aspect of the equation, one may additionally write

$$Si - Ci = Ai + Bi - 2C_{i+1} \dots \dots \dots (2)$$

Thinking about (2), one might imagine of a full adder as a shape whose operation depends on the carry o/p of the (i + 1)  $n^h$ th bit position (Ci + 1) and its entered operand bits. For this structure, the o/ps are the sum and the carry signals with the identical weights.

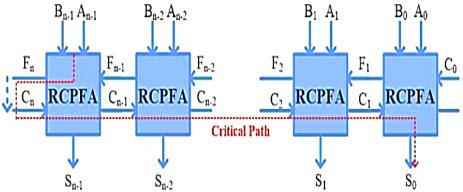

Based totally on the above dialogue, we advise a family of full adders for the RCPFA shown in Fig. 2. As shown in Fig. 2, those complete adders have 4 i/ps and three o/ps. The i/ps are the enter operands (Ai and Bi), the carry o/p of the subsequent bit position(Ci + 1), and a forecast signal (Fi). The RCPFA determines the summation result (Si), carry (Ci), and the forecast signal (Fi + 1) as its o/p alerts.

As declared prior to as, the advantage of the RCPA is that the worth of the error is within the trail of decrease among the bit significance. Which implies that the accumulative impact of the error (e.g., because of the delay model) within the route of the carry propagation is decrease for bits with higher significances

Fig.2 n-bit RCPA.

Available online at: http://www.jartms.org

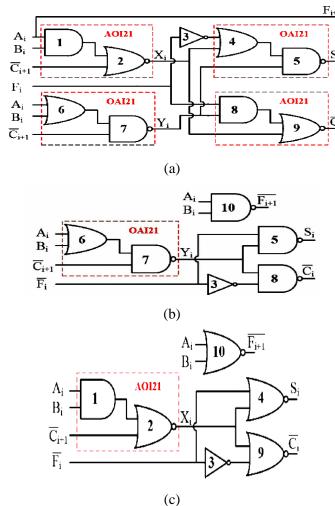

To determine a structure for RCPFA, the Karnaugh maps of the summation end result (Si) and carry (Ci)were drawn based totally on (2) and considering the forecast signal as an i/p (Fig. three) The Boolean contributors of the own family among i/ps for generating Si and Ci are obtained as

$$Si = C_{i+1}F_i + C_{i+1}Ai + C_{i+1}Bi + AiBiFi........(3)$$

$$Ci = C_{i+1}Fi + C_{i+1}\underline{Ai} + C_{i+1}\underline{Bi} + \underline{Ai}\underline{Bi}Fi..........(4)$$

Karnaugh maps for signals Si and Ci of the general form of RCPFA.

Primarily based on our requirement we design 3 styles of ReverseCarryPropagate adders the designs of those adders are given beneath. by using the use of these proposed adders we will put into effect 3 varieties of reverse propagate adders and are used in the vicinity of approximate adders that is proven on determine 1

Fig.4 Internal structures of the (a) RCPFA-D1,

(b) RCPFA-D2, (c) RCPFA-D3

DST Sponsored Three Day National Conference on "Sensor Networks, Internet of Things and Internet of Everything", 17 October 2019 to 19 October 2019 Organized by Department of EEE, Chadalawada Ramanamma Engineering College (Autonomous), A.P.

Available online at: http://www.jartms.org

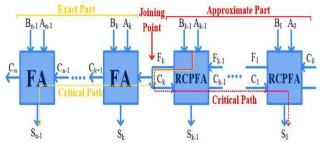

The architectural representation of an n-bit adder that is designed with the help of a ReverseCarryPropagate adder is shown below.

Fig.5 The figure depicts an n-bit adder with RCPA as mentioned earlier. If the carry propagates in the reverse or counter flow manner then the weights of the carry would decrease, this property helps having less vulnerability to the delay version (because of method and supply voltage versions) impact for this adder in comparison to other proposed approximate FAs. This is particularly effective inside the case of hybrid adders with large sizes for the approximate part which determines the crucial route of the adder. The proposed RCPFAs can be used in hybrid adders whose popular n-bit structure based totally at the RCPFAs are depicted in Fig. 8. Obviously, the design parameters of the adder rely on the width of the approximate component.

#### III. PROPOSED HYBRID ADDER

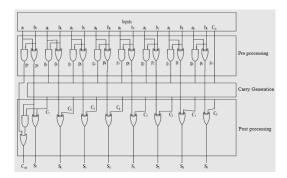

Here on this paper we advocate a brand new idea that's called as hybrid n-bit adder wherein we have two one-of-a-kind styles of n/2 bit adders are collectively to form an n bit adder. To enhance the general performance in phrases of delay we have a tendency to use a parallel prefix adder referred to as KoggeStone adder. The delay of an adder depends upon on however fast the carry reaches every bit operates. Therefore, the foremost problem within the layout of binary addition is that the carry chain as a result of the dimension of the input quantity will increase the length of the carry chain and delay can boom. To reduce the delay and to boost the performance, the parallel prefix adders will be utilized. The construct in parallel prefix adders is to reason a tiny low establishment of intermediate prefixes so find the large cluster prefixes, until all of the carry bits are calculated. Parallel Prefix addition of the operands A&B of width n is finished in 3 steps as given underneath

- 1. Pre-Processing

- 2. Internal Carry Generation

- 3. Post-Processing

#### Pre-processing stage:

Here in the 1<sup>st</sup> level, we shall calculate the (Gi) Generate-signals & (Pi) Propagate-signals, which are used to generate carry i/p of every adder. A&B are i/p's & there alerts are given by the equation one & two.

$$Pi = AiBi \dots (5)$$

$$Gi = Ai.Bi....(6)$$

Available online at: http://www.jartms.org

Fig.6 Overall architecture of Parallel prefix addition

# Carry generation stage:

Here in the 2<sup>nd</sup> level, as we know that we compute Gi & Pi signals and the computation flow is in parallel and it is identical for every bit. After the calculation of an extra bit named carry in parallel they can be divided into smaller portions. Carry operator contains 2 AND gates, 1 OR gate. It makes use of propagate and generate as intermediate indicators which might be given by the equations three & four.

$$P_{(i:k)} = P_{(i:j)} \cdot P_{(j-1:k)} \dots \dots (7)$$

$$G_{(i:k)} = G_{(i:j)} + (G_{(j-1:k)} \cdot P_{(i:j)}) \dots \dots (8)$$

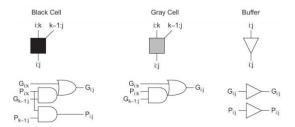

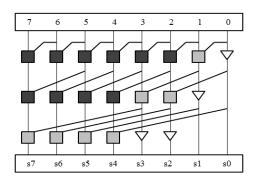

This carry is generated with the aid of the usage of different cellular structures known as Grey Cell, Black Cell and Buffer Cell. By way of the usage of this cell structures **we are going to** calculate final carry and are identical for all parallel prefix adders however the layout of carry generation is one in every of a sort. Fig.7 Black Cells, Gray Cells and Buffer cell used for carry generation stage

#### Post Processing:

This is the ultimate level; here the total bits are generated. The total bits are generated each with the helpful resource of using easy XOR gates or via the usage of conditional sum adders. In conditional total adders, for every bit role, tentative sums may be generated and also the best one is perhaps selected while the applicable carry for that bit arrives. KoggeStone prefix adder is one among the fast adder design, because of its very high performance it is used in VLSI implementations. Kogge-Stone adder has large area with minimal fan-out. The KoggeStone adder is extensively known as a parallel prefix adder that performs fast logical addition.

Available online at: http://www.jartms.org

Fig.8 Carry generation of an 8-bit Kogge stone adder

Proposed Adder architecture is shown in below figure

Fig.9 Proposed Hybrid adder architecture

# IV. RESULTS AND DISCUSSION

By imposing the adder with two sub adders like Kogge stone adder and Reverse Carry Propagate adder we will have better in terms of delay. Right here on this paper we present 16-bit and 32-bit adders with 3 one of a kind designs of Reverse Carry Propagate adders. The consequences are supplied within the beneath table.

Table 1 Comparison between Existing and proposed Adders

|          | Existing |        | Proposed |        |

|----------|----------|--------|----------|--------|

| Adder    | Area     | Delay  | Area     | Delay  |

| Type     |          |        |          |        |

| 16bit_d1 | 45       | 13.341 | 62       | 13.003 |

| 16bit_d2 | 34       | 13.322 | 50       | 10.982 |

| 16bit_d3 | 33       | 13.308 | 48       | 11.296 |

| 32bit_d1 | 95       | 21.829 | 148      | 22.461 |

| 32bit_d2 | 75       | 21.809 | 132      | 15.318 |

| 32bit_d3 | 80       | 21.765 | 137      | 16.296 |

DST Sponsored Three Day National Conference on

<sup>&</sup>quot;Sensor Networks, Internet of Things and Internet of Everything", 17 October 2019 to 19 October 2019 Organized by Department of EEE, Chadalawada Ramanamma Engineering College (Autonomous), A.P.

Available online at: http://www.jartms.org

## V. CONCLUSION

In this paper we have designed and carried out an n-bit adder with a hybrid architecture where we use 2 sorts of adders for implementation of large adder. We use approximation in decrease aspect addition this is least vast aspect and correct addition in better side this is most giant aspect. The accurate adder we used on this challenge is a parallel prefix adder referred to as Kogge stone adder and the approximate adder we used is the RCPA we proposed in this paper. With the aid of this architecture we are able to get better delay whilst degrading the accuracy and area.

#### REFERENCES

- [1] J. Kung, D. Kim, and S. Mukhopadhyay, "On the impact of energyaccuracy tradeoff in a digital cellular neural network for image processing," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 34, no. 7, pp. 1070–1081, Jul. 2015.

- [2] S. Mittal, "A survey of techniques for approximate computing," ACM Comput. Surv., vol. 48, no. 4, pp. 62-1–62-33, Mar. 2016.

- [3] A. B. Kahng and S. Kang, "Accuracy-configurable adder for approximate arithmetic designs," in Proc. 49th Annu. Design Autom. Conf. (DAC), Jun. 2012, pp. 820–825.

- [4] D. Mohapatra, V. K. Chippa, A. Raghunathan, and K. Roy, "Design of voltage-scalable meta-functions for approximate computing," in Proc. Design, Autom. Test Eur., Mar. 2011, pp. 1–6.

- [5] T. Moreau, A. Sampson, and L. Ceze, "Approximate computing: Making mobile systems more efficient," *IEEE Pervasive Comput.*, vol. 14, no. 2, pp. 9–13, Apr. 2015.

- [6] A. Madanayakeet al., "Low-power VLSI architectures for DCT/DWT: Precision vs approximation for HD video, biomedical, and smart antenna applications," *IEEE Circuits Syst. Mag.*, vol. 15, no. 1, pp. 25–47, 1st Quart., 2015.

- [7] N. Zhu, W. L. Goh, W. Zhang, K. S. Yeo, and Z. H. Kong, "Design of low-power high-speed truncation-error-tolerant adder and its application in digital signal processing," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 18, no. 8, pp. 1225–1229, Aug. 2010.

- [8] H. R. Mahdiani, A. Ahmadi, S. M. Fakhraie, and C. Lucas, "Bio-inspired imprecise computational blocks for efficient VLSI implementation of soft-computing applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 4, pp. 850–862, Apr. 2010.

- [9] K. P. Parker and E. J. McCluskey, "Probabilistic treatment of general combinational networks," *IEEE Trans. Comput.*, vol. C-100, no. 6, pp. 668–670, Jun. 1975.

- [10] A. Papoulis and S. U. Pillai, Probability, Random Variables and Stochastic Processes. New York, NY, USA: McGraw-Hill, 2002.

- [11] O. Akbari, M. Kamal, A. Afzali-Kusha, and M. Pedram, "Dual-quality 4:2 Compressors for utilizing in dynamic accuracy configurable multipliers," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 25, no. 4, pp. 1352–1361, Apr. 2017.

DST Sponsored Three Day National Conference on "Sensor Networks, Internet of Things and Internet of Everything", 17 October 2019 to 19 October 2019 Organized by Department of EEE, Chadalawada Ramanamma Engineering College (Autonomous), A.P.

Available online at: http://www.jartms.org

- [12] L. Wanhammar, DSP Integrated Circuits. New York, NY, USA: Academic, 1999.

- [13] NurdianiZamhariu, Peter Voon, and KuryatiKipli, "Comparision of Parallel Prefix Adder", Proceedings of the World Congress on Engineering, WCE, vol. 2, 2012

- [14] AungMyo San, Alexey N. Yakunin, "Reducing the Hardware Complexity of a Parallel Prefix Adder" 978-1-5386-4340-2/2018 IEEE

- [15] J. Sklansky, "Conditional-Sum Addition Logic," *IRE Transactions on Electronic Computers*, vol. EC-9, no. 2, pp. 226–231, June 1960.

- [16] B. Zeydel, D. Baran, and V. Oklobdzija, "Energy-Efficient Design Methodologies: High-Performance VLSI Adders," *IEEE Journal of Solid-State Circuits*, vol. 45, no. 6, pp. 1220–1233, June 2010.

#### **Author's Profile:**

**P.Ramya** received her B.Tech degree in Electronics and communication Engineering from sri venkateswara engineering college for women& technology for women, Tirupati (A.P), India. Currently pursuing her M.Tech degree in VLSI Stream at Chadalawada Ramanamma Engineering College, Tirupati(A.P), India. Her area of research Includes in Constructing the Blue Print of Rapid Reverse Converter through the Parallel Prefix Adder.

**Dr.V.Thrimurthulu** M.E.,Ph.D., MIETE., MISTE Professor & Head of ECE Dept. He received his Graduation in Electronics & Communication Engineering AMIETE in 1994 from Institute of Electronics & Telecommunication Engineering, New Delhi, Post Graduation in Engineering M.E specialization in Microwaves and Radar Engineering in the year Feb, 2003, from University College of Engineering, Osmania University, Hyderabad., and his Doctorate in philosophy Ph.D from central University, in the year 2012. He has done his research work on Ad-Hoc Networks.

**Ms.G.Dillirani** is currently working as Assistant Professor in the Department of Electronics & Communication Engineering at Chadalawada Ramanamma Engineering College, Tirupati, India. She has 7 years of teaching experience. Her's extensive education includes B.Tech from SIET Puttur, University, plus M.Tech in SIET Puttur, A.P, India. From JNTU Hyderabad. She is making research in the field of Biomedical Signal Processing.